Continuación del artículo "Organización de memoria en arquitecturas multicore".

Arquitecturas de memoria no uniforme.

Las arquitecturas de memoria no uniforme (NUMA por sus siglas en inglés) utilizan (como en SMP) un único espacio de direcciones, pero en este caso cada procesador es dueño de una parte de la memoria, a la cual puede acceder más rápido. Utiliza pasaje de mensajes escondido para el acceso a memoria remota.

En un entorno NUMA el programador puede acceder de forma transparente a cualquier posición de memoria y es el hardware quien crea esta abstracción.

Unas de las pioneras en tecnología NUMA fue la empresa Sequent Computer Systems, quien introdujo los sistemas de multiprocesamiento y diseño de memoria NUMA a comienzo de los ‘90. Luego fue adquirida por IBM y estos desarrollos fueron implementados en los procesadores Power.

La arquitectura análoga a la NUMA desarrollada por IBM fue denominada SE (Shared Everything por sus siglas en ingles). En la actualidad esta tecnología se encuentra integrada en los procesadores Power6, los cuales la heredaron de los Power4.

La tecnología desarrollada por Intel se denomina QuickPath Interconnect, incluye un controlador de memoria en el chipset y permite compartir toda la memoria física entre los procesadores de forma transparente para el Sistema Operativo. Cada procesador posee un enlace punto a punto de alta velocidad.

AMD implementó el sistema de acceso a memoria no uniforme (NUMA) que permite la conexión entre procesadores a través de enlaces de alta velocidad denominados Hypertransport Links. En este diseño cada procesador posee su propio controlador de memoria y su propia memoria local. Cuando el procesador accede a la memoria local, la latencia es baja; mientras que si intenta acceder a memoria remota (memoria alocada en otro procesador) la latencia es alta.

Cada uno de los procesadores está conectado entre sí a través de un enlace coherente de Hypertransport de alta velocidad. Cada procesador posee un enlace bidireccional no coherente para dispositivos de entrada-salida y dos enlaces bidireccionales coherentes, que permiten la conexión entre los procesadores.

Los accesos punto a punto permiten acceder a ciertas regiones de memoria de forma más rápida y penaliza el acceso a otras. Por ejemplo en una PC con 2 GB de memoria y dos procesadores, se podría privilegiar el acceso al primer GB para un procesador y el acceso al segundo GB para el otro procesador. Cada procesador tendría su propio controlador de acceso a memoria y ya no sería requerido un bus compartido por ambos procesadores.

Cada CPU en un sistema NUMA pueden acceder a dos tipos de memoria: memoria local y memoria remota. La memoria local es aquella que se encuentra en el mismo nodo que la CPU, que se accede con baja latencia, y la memoria remota se encuentra en otro nodo, en otra CPU. La CPU debería acceder a través del nodo de interconexión para la memoria remota, el cual presentaría una alta latencia.

Matias E. Vara

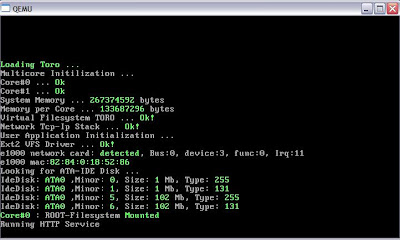

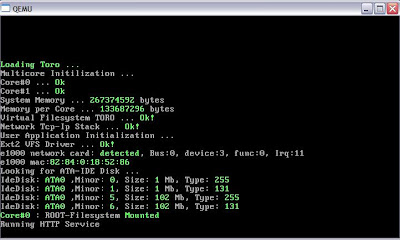

www.torokernel.org