Monday, December 12, 2011

Importante bug solucionado en la migración de threads

Thursday, August 25, 2011

Parcheando GDB 7.3 para debug remoto

Tuesday, August 23, 2011

Toro en el Congreso de Micro-electronica (UNLP)

Saturday, July 30, 2011

Toro en Ubuntu 11.04!

Friday, June 24, 2011

Toro bootloader

Wednesday, May 04, 2011

Mecanismos de comunicación entre procesos

Los spin-lock

Impacto del uso de spin-lock

Thursday, April 14, 2011

Protección de memoria en sistemas multicore

Introducción

Cuando se diseña un kernel para un sistema multicore la memoria compartida deberá ser protegida de accesos de escritura concurrentes. Las protecciones que utiliza el kernel incrementan la complejidad del código y decrementan el desempeño del SO.

Si uno o más procesadores acceden a los mismos datos al mismo tiempo, en el caso de sistemas multitarea debe cumplirse la exclusión mutua para proteger a los datos compartidos.

Para el caso de sistemas monoprocesadores multitarea apropiativos ocurre que cada cierto tiempo el planificador cambia de tarea, por lo tanto el único riesgo que se tiene es que mientras los datos están siendo modificados por un proceso, el planificador decida cambiar de tarea. La protección implementada en este caso es sencilla: simplemente se deshabilita el planificador mientras el proceso está en su zona crítica y luego se habilita nuevamente.

En sistemas con más de un procesador esta solución no puede ser implementada. Esto es debido a que los procesos se ejecutan en paralelo en los diferentes procesadores y puede existir otro proceso ejecutando la misma línea de código al mismo tiempo; por lo tanto de nada serviría inhabilitar el planificador del procesador local.

Metodos de proteccion de recursos

Para poder proteger recursos en sistemas con multiprocesamiento primero debemos definir operaciones atómicas. Estas son operaciones que si bien pueden estar constituidas por pasos más pequeños conforman un paquete indivisible de ejecución.

Operaciones atomicas

En los microprocesadores las operaciones tanto de escritura como de lectura tomadas de forma individual son siempre atómicas. Esto quiere decir que se garantiza que la operación terminará antes que cualquier otro procesador acceda a esa región de memoria.

Para ciertas operaciones el procesador utiliza el bloqueo del bus de memoria para controlar la lectura o escritura de una región. Para ello se proporciona la línea de control #Lock que es levantada cuando se realizan operaciones críticas de memoria. Mientras esta señal está en alto, las solicitudes provenientes de otros procesadores son bloqueadas.

El acceso al bus es no determinístico; esto quiere decir que el procesador que se quedará con el bus es el que llegue antes. Cada procesador compite con el resto, lo cual es un problema a medida que incrementamos el número de procesadores.

Pero ¿Por qué son necesarias las operaciones atómicas? Supongamos que queremos incrementar una variable contador, el código Pascal de esto sería:

contador = contador + 1 ;

Si esta línea se ejecuta simultáneamente en dos procesadores el resultado será incorrecto sino se utiliza protección.

El valor correcto de contador es 2 pero utilizando instrucciones que se realizan de forma atómica.

Al utilizar operaciones atómicas los procesadores se sincronizan para modificar de a uno la variable, y el resultado es correcto. El tiempo necesario para sincronizar la ejecución de la instrucción se incrementa con el número de procesadores que intentan acceder a la variable.

Impacto de las operaciones atomicas

La utilización de operaciones atómicas en sistemas con pocos procesadores no supone una gran carga para el sistema y es una solución rápida a problemas de memoria compartida; pero a medida que incrementamos el número de procesadores éstas se tornan en un cuello de botella.

Si suponemos una PC con 8 núcleos de 1.45 GHz cada uno [1], mientras que el tiempo consumido en promedio por instrucción es 0.24 ns, una instrucción de incremento atómico demora 42.09 ns.

Es claro que el tiempo consumido por las operaciones atómicas empieza a ser crítico.

[1] Paula McKenney: RCU vs. Locking Performance on Different Types of CPUs.

http://www.rdrop.com/users/paulmck/RCU/LCA2004.02.13a.pdf, 2005

www.torokernel.org

Tuesday, April 05, 2011

Organizacion de memoria en arquitecturas multicore: Conclusion.

Sunday, March 13, 2011

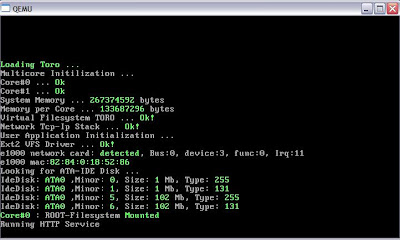

e1000 driver para TORO

Aquí les pongo un screen de la detección y lectura de la MAC, por ahora es lo que tengo en el SVN.

Saludos!.

Matias E. Vara

www.torokernel.org

Saturday, March 05, 2011

Organizacion de memoria en arquitecturas multicore II

Las arquitecturas de memoria no uniforme (NUMA por sus siglas en inglés) utilizan (como en SMP) un único espacio de direcciones, pero en este caso cada procesador es dueño de una parte de la memoria, a la cual puede acceder más rápido. Utiliza pasaje de mensajes escondido para el acceso a memoria remota.

En un entorno NUMA el programador puede acceder de forma transparente a cualquier posición de memoria y es el hardware quien crea esta abstracción.

Unas de las pioneras en tecnología NUMA fue la empresa Sequent Computer Systems, quien introdujo los sistemas de multiprocesamiento y diseño de memoria NUMA a comienzo de los ‘90. Luego fue adquirida por IBM y estos desarrollos fueron implementados en los procesadores Power.

La arquitectura análoga a la NUMA desarrollada por IBM fue denominada SE (Shared Everything por sus siglas en ingles). En la actualidad esta tecnología se encuentra integrada en los procesadores Power6, los cuales la heredaron de los Power4.

La tecnología desarrollada por Intel se denomina QuickPath Interconnect, incluye un controlador de memoria en el chipset y permite compartir toda la memoria física entre los procesadores de forma transparente para el Sistema Operativo. Cada procesador posee un enlace punto a punto de alta velocidad.

AMD implementó el sistema de acceso a memoria no uniforme (NUMA) que permite la conexión entre procesadores a través de enlaces de alta velocidad denominados Hypertransport Links. En este diseño cada procesador posee su propio controlador de memoria y su propia memoria local. Cuando el procesador accede a la memoria local, la latencia es baja; mientras que si intenta acceder a memoria remota (memoria alocada en otro procesador) la latencia es alta.

Cada uno de los procesadores está conectado entre sí a través de un enlace coherente de Hypertransport de alta velocidad. Cada procesador posee un enlace bidireccional no coherente para dispositivos de entrada-salida y dos enlaces bidireccionales coherentes, que permiten la conexión entre los procesadores.

Los accesos punto a punto permiten acceder a ciertas regiones de memoria de forma más rápida y penaliza el acceso a otras. Por ejemplo en una PC con 2 GB de memoria y dos procesadores, se podría privilegiar el acceso al primer GB para un procesador y el acceso al segundo GB para el otro procesador. Cada procesador tendría su propio controlador de acceso a memoria y ya no sería requerido un bus compartido por ambos procesadores.

Cada CPU en un sistema NUMA pueden acceder a dos tipos de memoria: memoria local y memoria remota. La memoria local es aquella que se encuentra en el mismo nodo que la CPU, que se accede con baja latencia, y la memoria remota se encuentra en otro nodo, en otra CPU. La CPU debería acceder a través del nodo de interconexión para la memoria remota, el cual presentaría una alta latencia.

Matias E. Vara

www.torokernel.org

Saturday, January 15, 2011

Organizacion de memoria en arquitecturas multicore

Organizacion de memoria en arquitecturas multicore

El sistema más común de multiprocesamiento utilizado en la actualidad es el de acceso uniforme a memoria (SMP por sus siglas en inglés).

En esta arquitectura cada procesador puede acceder a cualquier región de memoria independiente uno del otro. El acceso se realiza por un único bus compartido, o sea que cada procesador compite con el resto para escribir o leer. Los accesos se realizan de a uno por vez –es decir- que solo un procesador en un instante dado, puede utilizar al bus. Todos los procesadores son similares y tienen capacidades equivalentes. Todos los procesadores tienen el mismo tiempo de acceso a cualquier posición de memoria. En ambientes SMP el acceso a memoria por el programador es totalmente transparente.

El primer microprocesador de Intel con soporte para multiprocesamiento, fue el Pentium PRO en 1992. El bus utilizado para la interconexión de la CPU con la memoria fue denominado Front Side Bus (FSB desde ahora).

Este es un bus bidireccional muy simple; el costo es bajo y en teoría no hay límite acerca del número de procesadores que se pueden interconectar.

Este es un bus bidireccional muy simple; el costo es bajo y en teoría no hay límite acerca del número de procesadores que se pueden interconectar.El siguiente paso dado por Intel para incrementar el ancho de banda del FSB fue dividir el bus en dos buses independientes. Sin embargo el ancho de banda se vio reducido debido al tráfico que debía ser reenviado por todo los buses para mantener los caches coherentes.

En 2007 se implementó un bus dedicado por procesador.

A medida que se incrementaron el número de procesadores en las computadoras modernas también se incrementó el tráfico por el bus, convirtiéndolo en un cuello de botella y degradando la performance de la configuración SMP, fijando un límite entre 16 a 64 procesadores.

El FSB fue fuertemente criticado debido a que éste representa una barrera para las nuevas tecnologías emergentes multicore.

Mientras que una CPU puede ejecutar instrucciones rápidamente, esta velocidad será desperdiciada si no puede hacer la captura y decodificación de las instrucciones tan rápido como las ejecuta. Cuando ocurre esto la CPU debe esperar por lo menos un ciclo más de reloj hasta retornar el valor desde la memoria.

El FSB se comenzó a sustituir a partir de 2001 por dispositivos de acceso punto a punto como Hypertransport de AMD o QuickPath Interconnect de Intel, remplazándose el modelo de acceso uniforme por el modelo de acceso no uniforme.

Matias E. Vara

www.torokernel.org